Main control chip: RTL8852BE

Specifications: 2T2R

Speed: 300+866M

Interface: PCIE

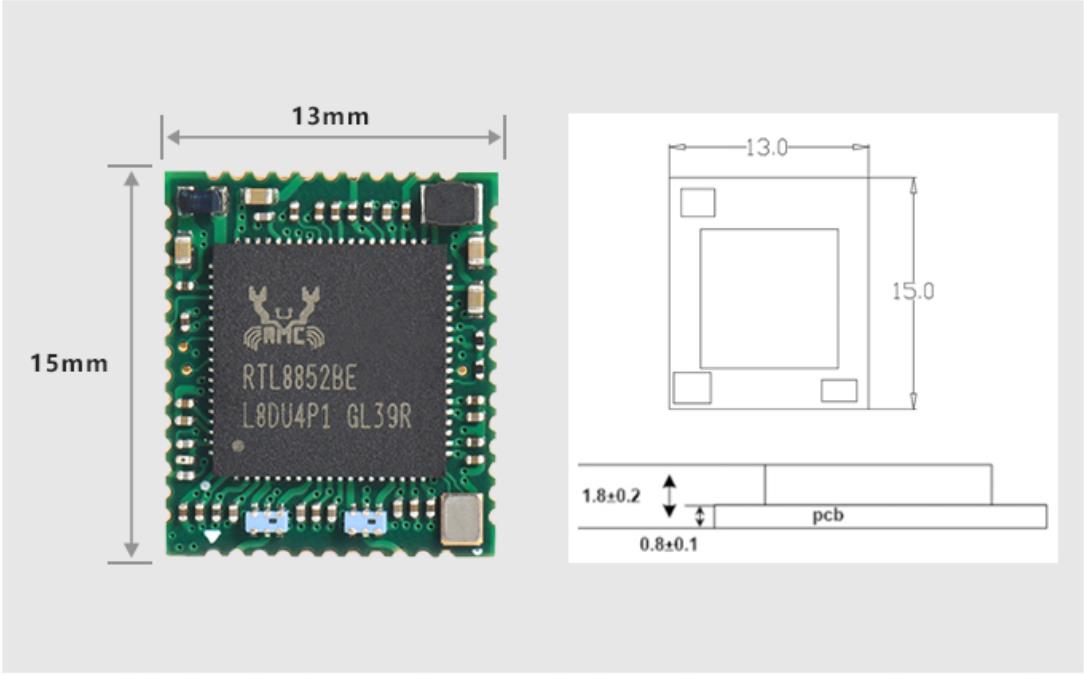

Size: 13*15*2.1mm (L*W*H))

Working voltage: 3.3V

Wireless standard: 802.11b/g/n/ac/ax+BLE5.2

Band width: 2.4G+5.8G

Working temperature: -20°C to +70°C

Features

■ Support Linux/Android operating system

■ Support Soft AP

■ Comply with CE/FCC/SRRC electromagnetic compatibility regulations

■ Follow RoHs/REACH environmental protection directives

■ Stamp hole package, easy to SMT process

■ Suitable for: IPC, smart TV, set-top box, driving recorder

Module size chart

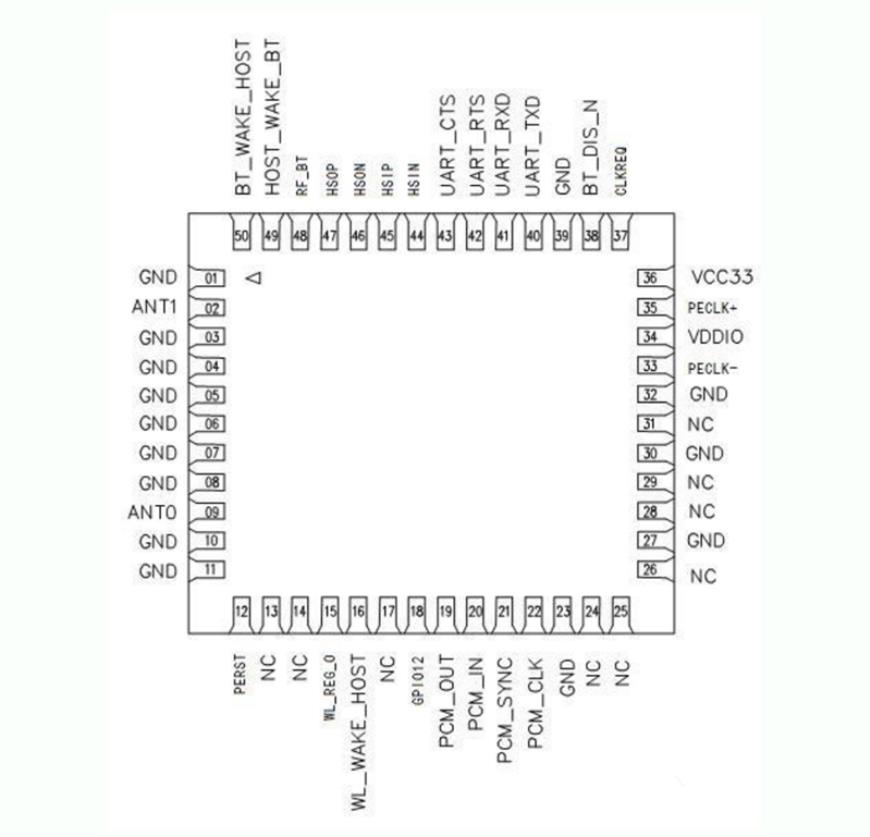

Module pin

| Pin | Name | Description |

| 1 3-8 10 11 25 27 30 32 39 | GND | Ground connections |

| 2 | ANT1 | RF I/O port chain1, Dual band Wi-Fi and BT(2 ant type) |

| 9 | ANT0 | RF I/O port chain0, dual band Wi-Fi |

| 12 | PERST | PCIE reset, active low |

| 14 | G_BT | GPIO5. G_BT If not used keep NC. Do not connect to GND. |

| 15 | SD_RESET | Reset Pin for SDIO interface ON: pull high; OFF: pull low Low for disable SDIO interface |

| 16 | WL_WAKE_HOST | GPIO10. WLAN to wake-up HOST |

| 17 | SDIO_CMD | SDIO command line |

| 18 | SDIO_ CLK | SDIO clock line |

| 19 | SDIO_DATA3 | SDIO data line 3 |

| 20 | SDIO_DATA2 | SDIO data line 2 |

| 21 | SDIO_DATA0 | SDIO Data line 0 |

| 22 | SDIO_DATA1 | SDIO data line 1 |

| 24 25 26 28 29 31 | NC | No connect |

| 33 | PECLK- | PCIE CLK- |

| 34 | VDDIO | I/O Voltage supply input 1.8V or 3.3V |

| 35 | PECLK+ | PCIE CLK+ |

| 36 | VCC33 | Main power voltage source input 3.3V |

| 37 | CLK REQ | PCIE clk request |

| 38 | BT_DIS_N | Enable pin for Bluetooth device Default ON: pull high; OFF: pull low |

| 40 | UART_TXD | Bluetooth UART interface |

| 41 | UART_RXD | Bluetooth UART interface |

| 42 | UART_RTS | Bluetooth UART interface |

| 43 | UART_CTS | Bluetooth UART interface |

| 44 | HSIN | PCIE RX- |

| 45 | HSIP | PCIE RX+ |

| 46 | HSON | PCIE TX- |

| 47 | HSOP | PCIE TX+ |

| 48 | RF_BT | BT antenna (opional if 3 ant type) 2 ant type NC this pin |

| 49 | HOST_WAKE_BT | HOST wake-up Bluetooth device |

| 50 | BT_WAKE_HOST | Bluetooth device to wake-up HOST |